## Laboratory 3 report

Cédric Hölzl Antoine Brunner

May 2020

#### 1 Introduction

The goal of this laboratory was to build a complete Linux system on a DE0-nano-SoC - a hybrid board consisting of a FPGA and an ARM dual-core HPS. Building a Linux system tailored to a specific hardware architecture is not an easy task, and there were a lot of steps involved before succeeding with that. First, we had to use the QSys platform designer to configure the hardware properly. Then, we had to use Altera's BSP editor to generate a boot loader tailored to the hardware configuration. After that, we had to compile the Linux OS and flash it to an SD card, along with the pre-loader and the boot loader. Finally, we could boot the system, and log onto it using a minicom terminal and after configuring the wired interface via SSH from a remote device.

## 2 Configuring the hardware using QSys

In this part, we had to configure the hardware for the Linux system. While the Linux system can run on an ARM processor, we still had to configure the FPGA part, because the goal was to reuse some hardware interfaces from previous labs. That is, we want to configure the joysticks and the thermal camera so that they can be used by the HPS. Figure 1 shows how we configured the system with the joysticks, the thermal camera and the ARM processor.

|     | System:                                          | soc_system Path: hp | s_0                          |                   | -         | -           |             |

|-----|--------------------------------------------------|---------------------|------------------------------|-------------------|-----------|-------------|-------------|

| Use | Connections                                      | Name                | Description                  | Export            | Clock     | Base        | End         |

| ~   |                                                  | 🖻 🖳 hps_0           | Arria V/Cyclone V Hard Proce |                   |           |             |             |

|     | $\sim \sim$                                      | memory              | Conduit                      | hps_0_ddr         |           |             |             |

|     | $\rightarrow \rightarrow$                        | hps_io              | Conduit                      | hps_0_io          |           |             |             |

|     |                                                  | h2f_reset           | Reset Output                 | Double-click to   |           |             |             |

|     | $  \rightarrow$                                  | h2f_lw_axi_clock    | Clock Input                  | Double-click to   | clk_0     |             |             |

|     |                                                  | h2f_lw_axi_master   | AXI Master                   | Double-click to   | [h2f_lw_a |             |             |

| ~   |                                                  | □ clk_0             | Clock Source                 |                   |           |             |             |

|     |                                                  | clk_in              | Clock Input                  | clk               | exported  |             |             |

|     |                                                  | clk_in_reset        | Reset Input                  | reset             |           |             |             |

|     | $   \rightarrow \rightarrow$                     | clk                 | Clock Output                 | Double-click to   | clk_0     |             |             |

|     |                                                  | clk_reset           | Reset Output                 | Double-click to   |           |             |             |

| ×   |                                                  | □ pwm_0             | pwm                          |                   |           |             |             |

|     | $    + + \rightarrow$                            | clock               | Clock Input                  | Double-click to   | clk_0     |             |             |

|     | $\bullet$ $+$ $+$ $\rightarrow$                  | reset               | Reset Input                  | Double-click to   | [clock]   |             |             |

|     | $  \downarrow \downarrow \downarrow \rightarrow$ | avalon_slave_0      | Avalon Memory Mapped Slave   | Double-click to   | [clock]   | 0x0004_9020 | 0x0004_902f |

|     |                                                  | conduit_end         | Conduit                      | pwm_0_conduit_end | [clock]   | _           |             |

| ×   |                                                  | □ pwm_1             | pwm                          |                   |           |             |             |

|     | $    \phi   \rightarrow$                         | clock               | Clock Input                  | Double-click to   | clk 0     |             |             |

|     | $  +   + + \rightarrow$                          | reset               | Reset Input                  | Double-click to   | [clock]   |             |             |

|     | $  \downarrow \downarrow \downarrow \rightarrow$ | avalon_slave_0      | Avalon Memory Mapped Slave   | Double-click to   | [clock]   | 0x0004_9010 | 0x0004_901f |

|     |                                                  | conduit_end         | Conduit                      | pwm_1_conduit_end | [clock]   |             |             |

| ~   |                                                  | ⊡ mcp3204_0         | mcp3204                      |                   |           |             |             |

|     | $    + \rightarrow$                              | clock               | Clock Input                  | Double-click to   | clk_0     |             |             |

|     | $\bullet$ $+$ $+$ $\bullet$ $\rightarrow$        | reset               | Reset Input                  | Double-click to   | [clock]   |             |             |

|     | $  +   \rightarrow$                              | avalon_slave_0      | Avalon Memory Mapped Slave   | Double-click to   | [clock]   | 0x0004_9000 | 0x0004_900f |

|     |                                                  | conduit_end         | Conduit                      | mcp3204_0_condui  | [clock]   | _           | _           |

| ~   |                                                  | □ lepton_0          | lepton                       |                   |           |             |             |

|     | $     \bullet   \rightarrow$                     | clock               | Clock Input                  | Double-click to   | clk_0     |             |             |

|     | $  \bullet   \bullet   \rightarrow$              | reset               | Reset Input                  | Double-click to   | [clock]   |             |             |

|     | $\bullet \longrightarrow$                        | avalon slave 0      | Avalon Memory Mapped Slave   | Double-click to   | [clock]   |             | 0x0004 7fff |

Figure 1: Overall view of the system

As a side note, since the HPS would run a Linux OS, accessing the memory mapped peripherals cannot be done in the virtual address space of the processes. Several solutions exists, such as creating a driver, or probably simpler, using *mmap* to map physical pages into the virtual address space. That was not the concern of the lab, but it is worth mentioning it, because that's a problem we will face in the next laboratory.

An error that we made while using QSys was that we didn't understand what the *peripheral multiplexer* tab was doing. Due to that misunderstanding, we did not select the pins that system needed, and couldn't boot the system correctly. After an explanation by an assistant, we finally understood how that pin multiplexer works, and we could fix the mistake that we had made.

Other than that, we also had to instantiate the system in the top-level VHD file, by making the right pin assignments for all the components, and get the design to compile. We also had some problems at this stage. Initially we left some pins unassigned by mistake, causing the fitter to fail, but that was easily fixed.

#### 3 Compiling the system

To compile the system on the board, we still had a long way. We had to generate the pre-loader using the BSP editor. After that, we downloaded Alteras's U-boot, configured it for the ARM processor and compiled it. The last piece of the puzzle was to download Ubuntu 14, compile it, and configure it by creating scripts that would run at the first start.

Although we have not succeeded initially in doing those steps by ourselves, we didn't encounter any major problems in those steps, thanks to the Soc-FPGA Design Guide.

The final step was to put all the generated files in the right partitions of the SD card, so that the system could properly boot: the pre-loader to the A2 partition, the boot loader to the FAT32 partition and the Linux file system to the EXT3 partition.

We were already familiar with creating partitions and moving data to certain partitions using the command line, so we managed to do this step without major difficulties.

### 4 Problems encountered

Of course, it would have been to easy if everything went correctly... We didn't manage to boot our system from the first time because of a very dumb mistake. At least, we have learnt something from that mistake.

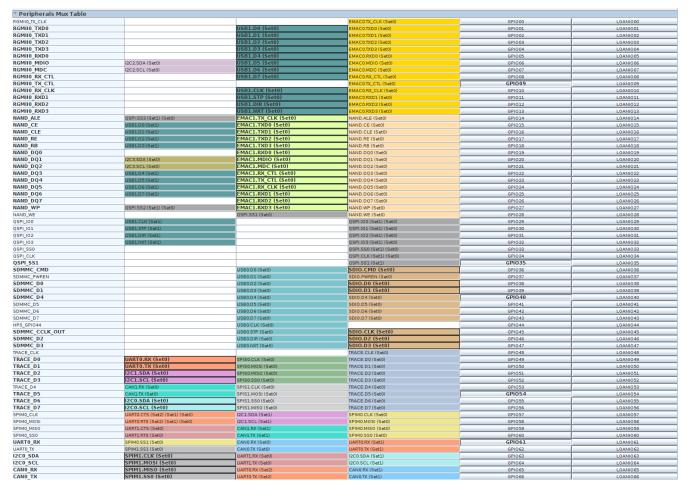

The mistake that we did is that we forgot to enable the GPIO pins in the QSys platform designer, meaning that the multiple ports (SD, Ethernet, ...) would never be properly connected to the processor. Figure 2 shows the interface on which we should have selected the right pins. That was the reason why we could not see anything in the Minicom terminal when the system was supposed to be booting. That mistake came from the fact that we didn't understand the QSys interface very well, nor the utility of the pin multiplexer. After an explanation from one of the assistants we have now understood what this interface is useful for, and we managed to fix the problem pretty easily.

Figure 2: The peripherals multiplexer view

# 5 Conclusion

As a conclusion, we think that this lab was a lot about following the guide, which sometimes didn't help us understand what we were doing. This in part the reason why we have made that mistake. Fortunately, it allowed us to question what we had done, and to learn what we were doing wrong. We had to restart the instruction from the beginning (having had a corruption issue with the VM), so the second time we started to remember a lot better what to do, allowing us to complete it quickly without issues.